В данной статье мы рассмотрим микропроцессорные блоки релейной защиты с точки зрения упрощения чтения логических схем. Статья будет полезна специалистам в области релейной защиты, которые только начинают знакомиться с микропроцессорной техникой.

О чем данная статья

Принципиальная электрическая схема — это самый краткий способ объяснить принципы работы устройства. Ведь описывать словами схемы, во-первых, трудоемко, а во-вторых, описание словами ведет к двоякому восприятию, тогда как любая схема жестко прописывает алгоритм работы.

На сегодняшний день, по разным оценкам, доля электромеханических реле, находящихся в эксплуатации, составляет от 70 до 80% от общего числа релейных устройств. Но с каждым днем количество микропроцессорных блоков релейной защиты растет, что приводит в шок специалистов эксплуатации, так как им приходится разбираться с работой новых устройств защиты. Данная реакция обусловлена в основном новизной и недоверием к блокам, а также необходимостью обучения и понимания работы микропроцессорных блоков релейной защиты. В процессе изучения работы блоков возникает проблема: для того чтобы разобраться, как работает блок, нужно для начала научиться читать логические схемы.

В данной статье я попробую объяснить, как не бояться таких схем, как упростить процесс их чтения, на что обращать внимание. Я не обещаю, что вы сразу научитесь читать схемы (это вопрос практики), а просто поделюсь основными методами, которые когда-то для себя выработал.

Логические схемы

Принципиальные электрические схемы для релейной защиты, выполненной на электромеханической элементной базе, представляют собой электрические связи между органами управления, различными реле и исполнительными механизмами. При чтении таких схем мы моделируем процессы замыкания/размыкания контактов, подачи напряжения на различные реле, срабатывания этих реле, таким образом мы как бы прослеживаем процесс движения напряжения от источника к приемнику. Как ни странно, но при чтении логических схем мы будем пользоваться этим же методом.

Логические схемы — это весьма сжатый способ представления информации о работе алгоритмов блока. В микропроцессорных устройствах релейной защиты нет промежуточных реле, нет электрических связей между реле, весь данный процесс выполняется в виде программы в процессоре блока, работающей по определенным алгоритмам. Графическое представление работы алгоритмов блока выполняется в виде логических схем, которые приводятся производителями блоков в руководствах по эксплуатации.

Для упрощения понимания логических схем попробуем провести аналогию между работой логических элементов и работой электрической схемы, выполненной на электромеханических реле и контактах.

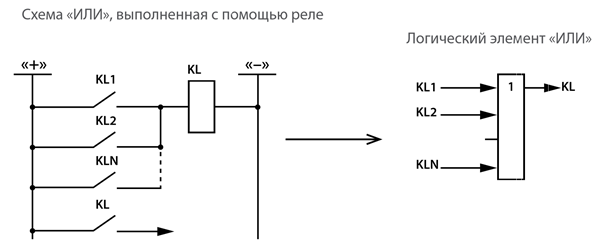

Логический элемент «ИЛИ»

Логическое «ИЛИ», или «логическое сложение», представляет собой обработку сигналов по схеме параллельного соединения. Само название этого элемента говорит нам о принципе его работы. На рис. 1 приведена схема реализации обработки сигналов с помощью реле KL, а также логический элемент «ИЛИ», который логически повторяет схему.

Рассмотрим логический элемент «ИЛИ» подробнее, так как рассуждения, относящиеся к данному элементу, можно будет отнести и к другим элементам, рассматриваемым ниже. Как видно из обозначения элемента, у него есть входные сигналы, располагающиеся слева от элемента, и выходные сигналы, располагающиеся справа. Входные и выходные сигналы – это логические состояния данных связей. В логических схемах есть два логических состояния — «0» или «1». Логическое состояние «0» — это отсутствие сигнала, а логическое состояние «1» — наличие сигнала. Если провести аналогию со схемой «ИЛИ», выполненной на реле, то состояние логической «1» —это замыкание контакта, например, KL1. Для более глубокого понимания следует уточнить, что контакт KL1 замыкается при срабатывании какого-то реле, не обозначенного в данной схеме, т.е. контакт сообщает нам, в каком состоянии находится реле (в сработавшем или нет). Получается, что логическое состояние «1» входного сигнала KL1 элемента «ИЛИ» — это срабатывание реле, не обозначенного на схеме, а логическое состояние «0» — это несрабатывание реле.

На данном этапе мы должны запомнить:

- В логических схемах у сигнала есть два состояния — «1» или «0».

- Входной сигнал логического элемента есть результат состояния предыдущего элемента.

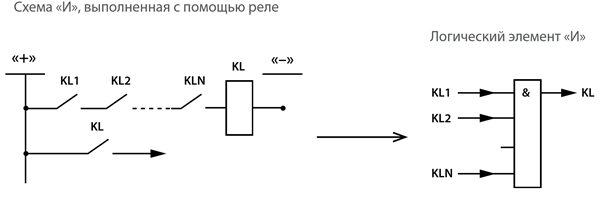

Логический элемент «И»

Логическое «И», или «логическое умножение», представляет собой обработку сигналов по схеме последовательного соединения. На рис. 2 приведена схема реализации обработки сигналов с помощью реле KL, а также логический элемент «И», который логически повторяет схему.

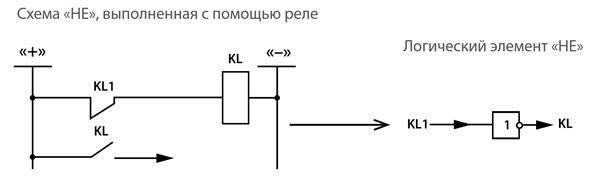

Логический элемент «НЕ»

Логическое «НЕ», или «инверсия», представляет собой элемент, который изменяет входной сигнал на противоположное состояние. Если на входе присутствует логическая «1», то на выходе будет логический «0», и наоборот, если на входе «0», то на выходе будет «1». На рис. 3 приведена схема реализации обработки сигналов с помощью реле KL, а также логический элемент «НЕ», который логически повторяет схему.

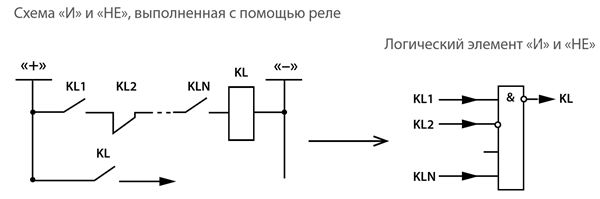

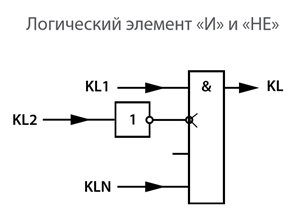

Очень часто логический элемент «НЕ» не обозначается на схемах как отдельный самостоятельный элемент, а указывается его сокращенное обозначение. На рис. 4 приведен пример логической схемы с элементом «И» и элементом «НЕ» на входе KL2.

Элемент «НЕ» обозначен как круг на входе KL2. Такое обозначение может встречаться на различных элементах, причем как на входе сигнала, так и на выходе. Такое сокращенное обозначение элемента «НЕ» очень часто применяется в логических схемах. Если вы только начинаете учиться читать такие схемы, рекомендую дорисовывать на входе элемент «НЕ» (как показано на рис. 5), так будет проще анализировать элемент «И» и элемент «НЕ».

Логические элементы «И», «ИЛИ», «НЕ» являются основными «рабочими лошадками» схем, и поэтому их надо хорошо понимать и правильно называть.

Элементы «И» и «ИЛИ» обычно называют, указывая количество входных сигналов: если элемент «ИЛИ» имеет 2 входа, то «2-ИЛИ» (произносится «два или»), если элемент «И» имеет 4 входа, то «4И» (произносится «четыре и»).

Если же на входах или выходах элемента «И» и «ИЛИ» выполнена инверсия (рис. 4), то обозначение инверсии присоединяют к имени элемента в начале для входа и в конце — для выхода. Т.е. элемент, показанный на рис. 4, имеющий 4 входа, можно назвать «4-НЕ-И» (произносится «четыре не и»), но чаще применяют просто «4-И» (т.к. из названия не ясно, на каком именно входе выполнена инверсия). Если инверсия выполнена на выходе элемента «И» с тремя входами, то такой элемент называют «3-И-НЕ» (произносится «три и не»).

Логический элемент RS-триггер

Триггер (или «защелка») представляет собой элементарную ячейку памяти. Триггер кардинально отличается от рассмотренных ранее логических элементов тем, что его выходной сигнал зависит не только от входных сигналов в данный момент времени, но и от его собственного предыдущего состояния.

Существует большое количество разнообразных триггеров. Рассмотрим наиболее распространенный тип триггера — RS-триггер, применяемый в микропроцессорных блоках релейной защиты.

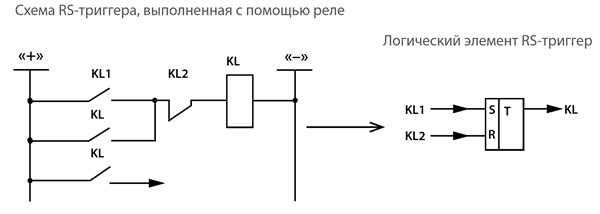

Логический элемент RS-триггер представляет собой элемент, который изменяет свое состояние: по сигналу «S» (Set — установить) — переходит в единицу, по сигналу «R» (Reset — сбросить) — в ноль. При подаче «1» на вход «S» на выходе будет «1», при подаче «1» на вход «R» на выходе будет «0».

Если на входы «S» и «R» ничего не подано (т.е. поданы нули), то выход триггера сохранит свое предыдущее состояние.

Остается два вопроса: что будет, если подать единицы одновременно на «S» и на «R», и какое состояние имел триггер в первый момент времени, т.е. при включении блока? Однозначного ответа на эти вопросы нет.

Первый вопрос называется «приоритет». Может быть «приоритет по S» (триггер «взведется», «встанет в единицу») и «приоритет по R» (триггер «сбросится», «обнулится»).

Второй вопрос называется «начальное состояние». Оно может быть «нулевое», может быть «единичное», а еще может быть энергонезависимое (которое запоминается и восстанавливается после включения блока). Энергонезависимое начальное состояние обычно устанавливают «нулевое», хотя возможны варианты.

Оба эти вопроса влияют на работу схемы, и варианты решения выбираются разработчиком обдуманно, в зависимости от того, что реализуется.

Как же узнать, какой именно триггер применен в схеме? Во-первых, надо посмотреть внимательно на его условное обозначение. Часто обозначение приоритетного входа выделяют особо (скобками или шрифтом), а начальное состояние записывают символом в нижней части графического обозначения («0», «1» или «M» — для энергонезависимого, от Memory — память). Если таких особых обозначений нет, то следует уточнить работу триггеров конкретного производителя в приложении к руководству по эксплуатации (как правило, приложение называется «Элементы функциональных схем»). На рис. 6 приведена схема реализации обработки сигналов с помощью реле KL, а также логический элемент RS-триггер, который логически повторяет схему.

Следует отметить, что данная схема определяет триггер «с приоритетом по R» и нулевым начальным состоянием: при наличии на входах KL1 и KL2 логических «1» на выходе будет логический «0».

Таймеры

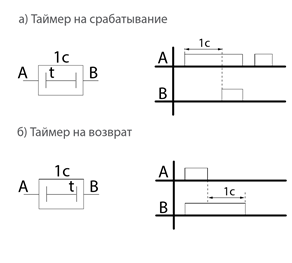

Наиболее распространены два типа таймеров: таймер с задержкой на срабатывание и таймер с задержкой на возврат (замедление, или «подхват» при отключении). Не будем подробно на них останавливаться, так как логика их работы повторяет логику работы электромеханических реле (например, РВ-238). На рис. 7 приведена диаграмма работы таймеров.

Производители на своих схемах могут применять разные условные графические обозначения (УГО) для описанных выше элементов. УГО, основанные на западных стандартах, кардинально отличаются от принятых в России. Во всех случаях объяснение непонятных обозначений следует искать в технической документации производителя.

Анализ схемы

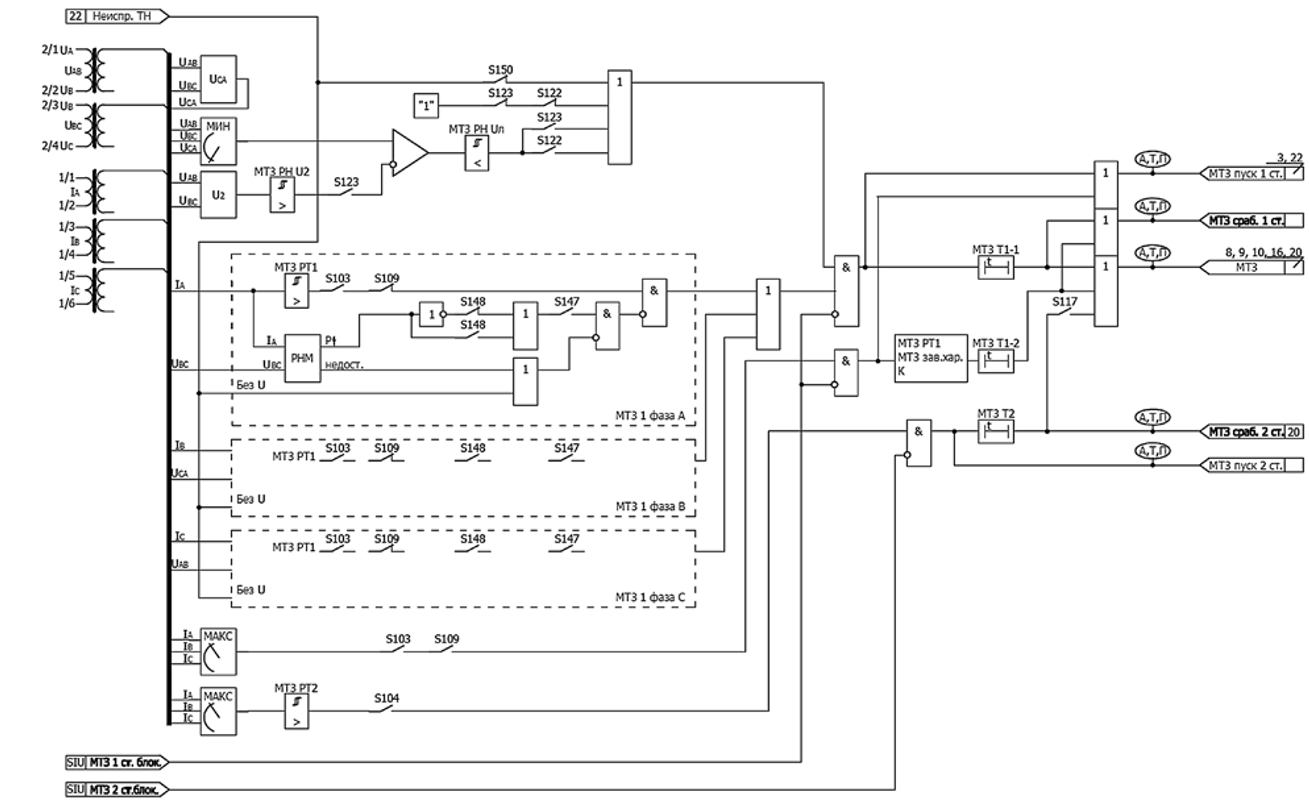

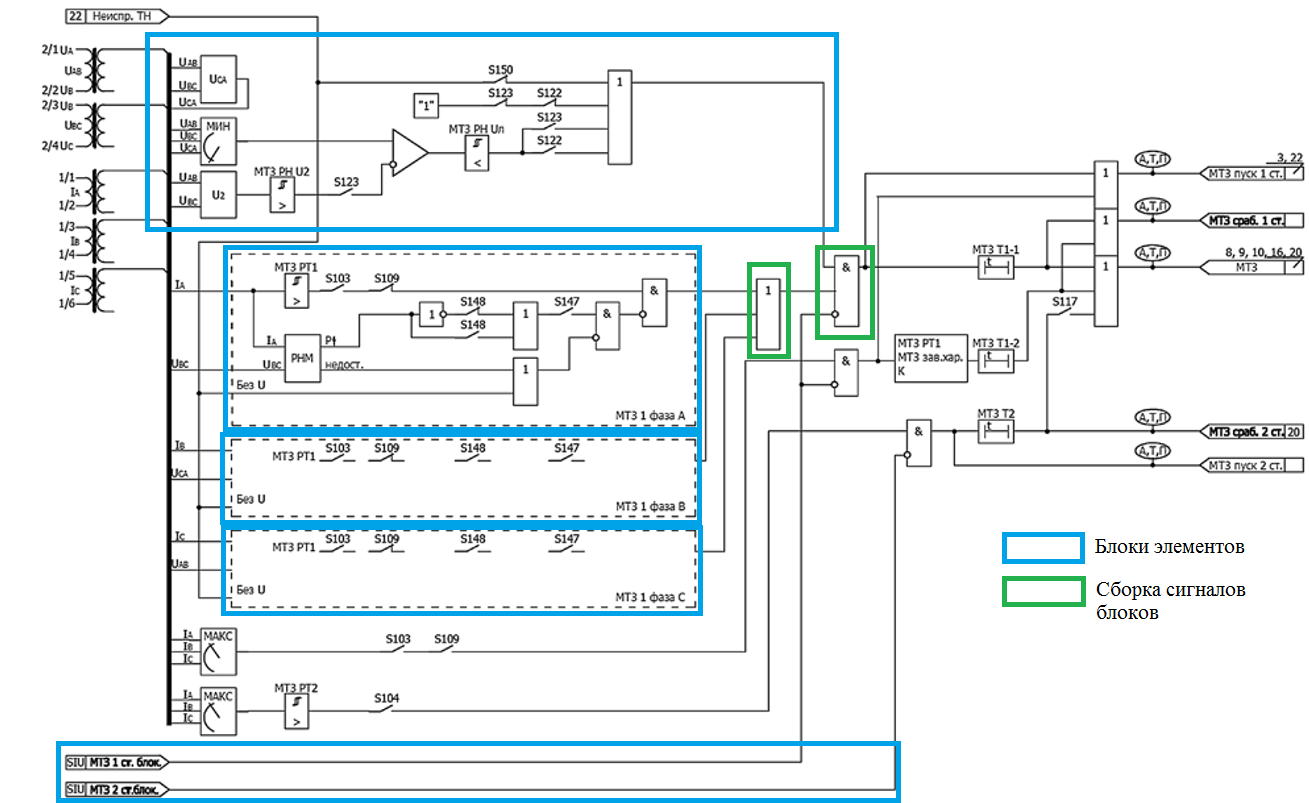

Мы познакомились с работой основных элементов, применяемых в логических схемах микропроцессорных блоков релейной защиты. Перейдем к чтению и анализу алгоритмов на примере логической схемы максимальной токовой защиты блока БМРЗ-152-ВВ-01 (производства НТЦ «Механотроника»). На рис. 8 приведена схема данного алгоритма.

Рассмотрим алгоритм работы первой ступени максимальной токовой защиты с независимой времятоковой характеристикой. Анализ любой схемы рекомендуется начинать с определения, что является входными и выходными сигналами. В данном примере входными сигналами являются логические сигналы: «Неиспр. ТН» (он приходит со схемы 22), назначаемые сигналы «МТЗ 1 ст. блок.» и «МТЗ 2 ст. блок.», а также аналоговые сигналы токов и напряжений. Выходными сигналами являются логические сигналы «МТЗ пуск 1 ст.», «МТЗ сраб. 1 ст.», «МТЗ», «МТЗ пуск 2 ст.» и «МТЗ сраб. 2 ст.». Так как мы анализируем первую ступень МТЗ, то сигналы «МТЗ пуск 1 ст.» и «МТЗ сраб. 1 ст.» и есть результат работы алгоритма и наша отправная точка. В качестве следующего шага поделим схему на блоки по принципу обобщения сигналов на логических элементах (рис. 9).

После данного обобщения (группировки) видно, что сигналы со всех блоков проходят через два логических элемента — «3-ИЛИ» и «3-И» (элементы выделены зелеными прямоугольниками). Далее попробуем проанализировать входные сигналы данных элементов и отбросить блоки, анализ работы которых можно выполнить отдельно.

Начнем с первого входа элемента «3-И» (рекомендую всегда начинать с элемента, который ближе всего находится к результату алгоритма, у нас это сигналы «МТЗ пуск 1 ст.» и «МТЗ сраб. 1 ст.»): сигнал приходит от блока, при небольшом анализе которого видно, что, если не вводить программные ключи (S122 и S123, то есть не размыкать эту цепь), то всегда на выходе данного блока будет логическая «1». Получается, что работу этого блока можно рассмотреть позже.

Сигнал на второй вход элемента «3-И» приходит с выхода элемента «3-ИЛИ», небольшой анализ которого показывает, что состояние сигнала зависит от многих условий, и тут необходимо делить схему на блоки. Запомним это.

Сигнал на третий вход элемента «3-И» приходит от входного сигнала «МТЗ 1 ст. блок.». По названию сигнала можно догадаться, что это блокировка первой ступени МТЗ по логическому сигналу. Так как третий вход элемента «3-И» инверсный, то отсутствие сигнала на данном входе не отражается на работе элемента «3-И». Разобраться с назначением и применением сигнала «МТЗ 1 ст. блок.» можно позже.

Анализ элемента «3-И» показывает, что основным сигналом данного элемента является сигнал, поступающий на второй вход, который приходит с выхода элемента «3-ИЛИ».

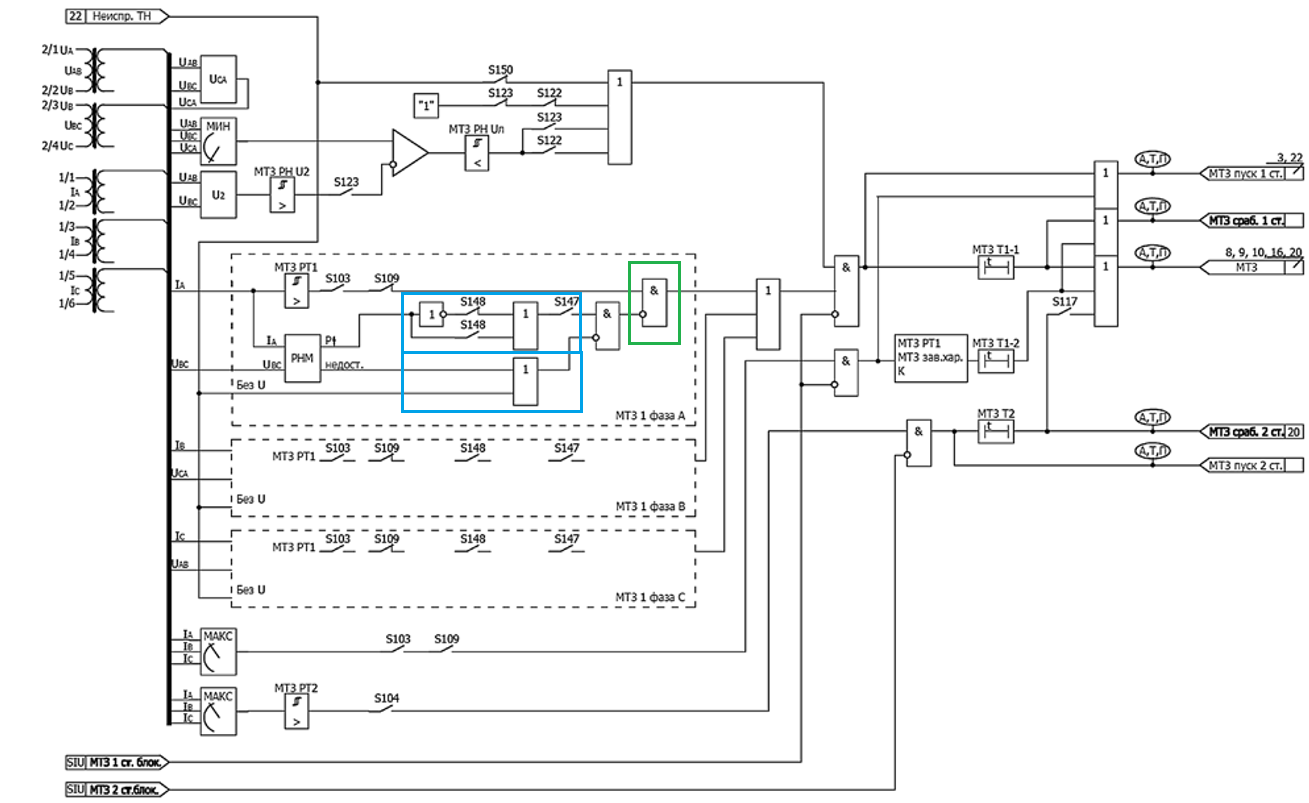

Как видим, элемент «3-ИЛИ» объединяет сигналы с трех блоков, которые отличаются только разными входными аналоговыми сигналами, а полный алгоритм работы блока показан в схеме обработки тока фазы А и напряжения BC (МТЗ 1, фаза А). Для анализа данного блока повторно проделаем операцию обобщения (группировки), как показано на рис. 10.

Как и в предыдущем анализе блоков, начнем анализ справа, с элемента «2И» (выделен зеленым прямоугольником). Сигнал на первый вход данного элемента приходит с компаратора «МТЗ РТ1» через программные ключи (программные накладки) S103 и S109. Анализ сигнала, поступающего на второй вход элемента (инверсный), показывает, что если не вводить программный ключ S147, то блоки, выделенные синими прямоугольниками, не влияют на работу элемента «2-И». Анализ этих блоков можно провести позже.

Поделив схему на блоки и убрав из анализа блоки, которые можно рассматривать отдельно, мы пришли к выводу, что работа первой ступени МТЗ связана с компаратором «МТЗ РТ1», программными ключами S103, S109 (рис. 11). Для ввода в работу первой ступени МТЗ необходимо ввести программный ключ S103 (S109 должен быть выведен) и подать на компаратор ток больше уставки «МТЗ РТ1». Анализ алгоритма работы первой ступени МТЗ закончен.

Анализ блоков, которые мы не рассматривали, я предлагаю вам провести самостоятельно.

Обобщим порядок анализа:

- Определяем входные и выходные сигналы.

- Делим схему на блоки по принципу обобщения сигналов на логических элементах.

- Анализируем входные сигналы каждого элемента, приходящие с блоков.

- Блоки, анализ работы которых можно провести позже, рассмотрим позже.

- Блоки, анализ работы которых невозможно отложить, делим на более мелкие блоки и проводим анализ.

- Находим компараторы или сигналы, влияющие на работу алгоритма, определяем кратчайший путь движения сигналов от входов до выходов.

- Анализируем блоки, указанные в п. 4, согласно пунктам 5 и 6.

Заключение

Проанализировав несколько схем, вы со временем забудете о преобразовании логических элементов в релейно-контактные схемы и усвоите следующие положения:

- сигнал есть — значит «1», сигнала нет — значит «0», и третьего не дано;

- нельзя просто так взять и соединить вместе выходы двух логических элементов (кстати, почему?);

- существуют и применяются другие логические элементы и другие триггеры, а не только те, о которых тут рассказано;

- инверсный вход элемента «И» преимущественно используется для блокировки остальных входных сигналов;

- все логические сигналы можно условно разбить на три группы: сигналы срабатывания (которые идут от компараторов или иных источников к главному выходу), сигналы разрешения (которые приходят на вход элемента «И» и разрешают пройти другому сигналу) и сигналы блокировки (которые приходят на инверсный вход элемента «И» и запрещают пройти другому сигналу);

- элемент «2-НЕ-И», у которого все входы инверсные, можно заменить на элемент «2-ИЛИ-НЕ», и наоборот, элемент «2-НЕ-ИЛИ» можно заменить на элемент «2-И-НЕ».

Автор:

Илья Иванов

Компания: НТЦ «Механотроника»

Должность: Начальник отдела РЗА

Источник: http://digitalsubstation.com

Отправляя сообщение, Вы разрешаете сбор и обработку персональных данных.

Политика конфиденциальности.